|

| [2015-10-30] |

Protocol Analyzer JTAG 2.0_V1.11.00 Release |

|

Modified Function 1. The Bit Length of Capture IR/DR that selected value range from 1 to 10 and the default is 1 is modified as selected value range from 1 to 20 and the default is 1. Before modified: The Bit Length of Capture IR/DR that selected value range from 1 to 10 and the default is 1. After modified: The Bit Length of Capture IR/DR that selected value range from 1 to 20 and the default is 1. 2. Add the selection of decoding first packet as Run_Test/Idle. Before modified: Decoding first packet has not the selection of Run_Test/Idle. After modified: Add the selection of decoding first packet as Run_Test/Idle. 【DOWNLOAD】

|

|

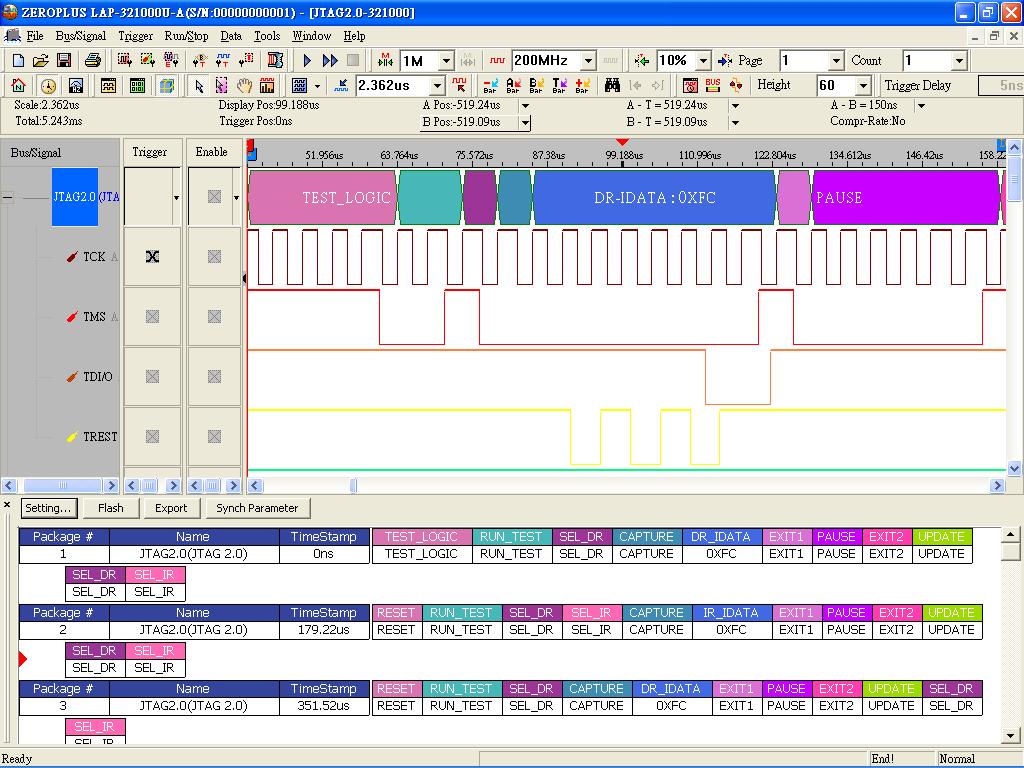

There are five signal lines for JTAG Bus , the content as below : TCK: Synchronous Clock TDI: Input Data TDO: Output Data TMS: State Selection TREST: Reset Machine It is easy for user to clearly see the state of TEST_LOGIC,RUN_TEST,SEL_DR in the JTAG Bus through the display mode of cob , according to the Special Bus Analysis Function of Zeroplus Logic Analyzer, there is no need the action of starting manual decoding according to waveform , it can speed up the speed of products development and save the time of products debug . more ~ |

|

|

|