杂讯滤波设定

使用逻辑分析仪内部取样测量汇流排数值,出现误差!

|

当使用逻辑分析仪内部取样测量汇流排数值时,因非同步取样而造成汇流排数值出现误差,您该怎么办? 这时,您就可以使用孕龙逻辑分析仪的‘杂讯滤波设定’功能将误差数值滤除哦!

适用:研发硬体环境上,本身存在一些杂讯问题却又无法即时将硬体上的杂讯去除,当下又想得到正确的汇流排数值,这个时候!就是使用汇流排宽度过滤功能的机会了! 经由孕龙逻辑分析仪,设定好过滤的宽度时间,即可得到正确的汇流排数值。

|

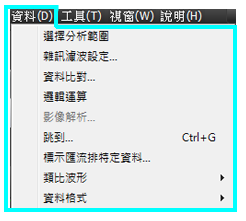

图一: 资料ToolBar下

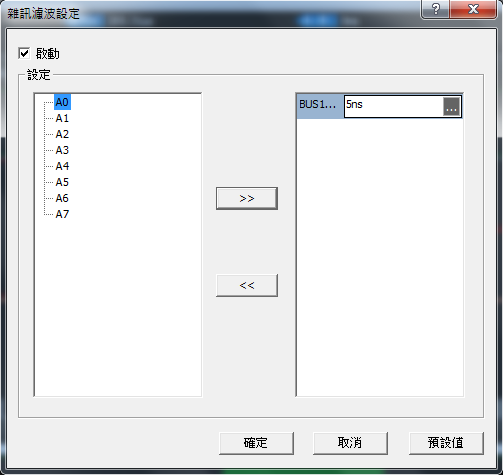

图二: 杂讯滤波设定 (Bus or 单一通道选择)

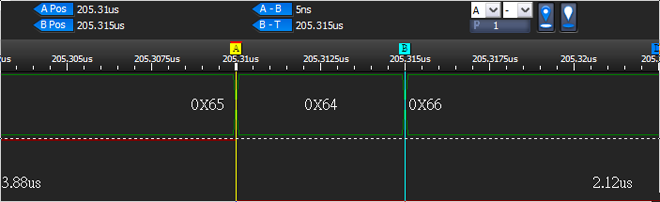

图三: 杂讯滤波设定 - 未启动 ( 0x64为杂讯)

|

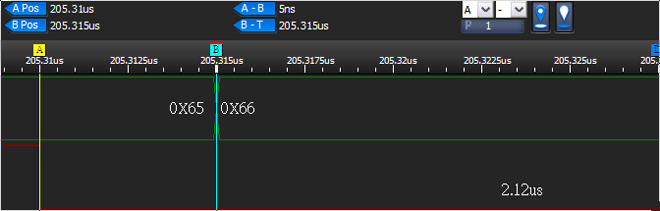

使用‘杂讯滤波设定’功能将误差数值滤除。 |

图四: 杂讯滤波设定 – 启动5ns杂讯滤波 (0x64被滤除)

|

|

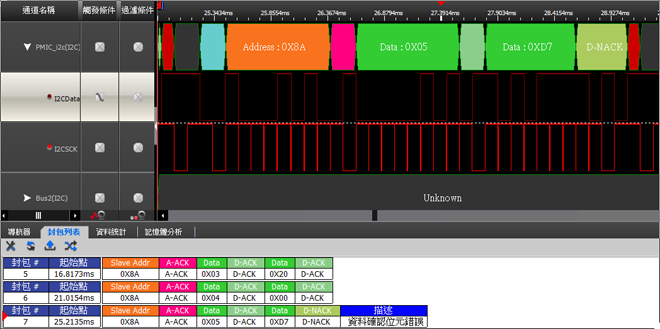

当某一I2C讯号状态在某一状况突然下出现解出data N-ACK造成资料确认位元错误时,我们可以查看CLK与 DATA打出波形是否正确,如图一 |

图一: 第七封包有异常状态

|

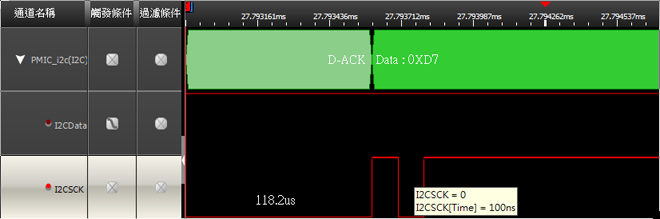

确认CLK信号缘时发现CLK多打出一次,判断可能为杂讯干扰,这时就可使用汇流排的宽度过滤来把此一杂讯过滤掉,如图二所示 |

图二: Data 0xD7出现100ns杂讯干扰

|

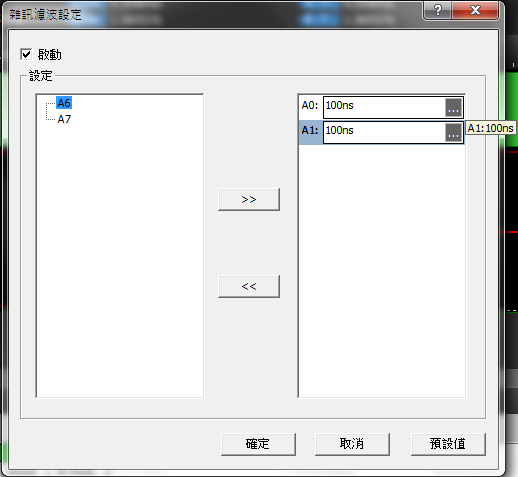

设定杂讯滤波,并把条件设为100ns,如图三所示 |

图三: 设定宽度过滤条件

|

设定完成后,Data资料就完整解码,如图四所示 |

图四: 杂讯问题解除

|