Quad SPI(Quad Serial Peripheral Interface)是一種高效的串列通訊協定,廣泛應用於微控制器(MCU)與外部快閃記憶體(Flash)之間的高速資料傳輸。相較於傳統SPI,Quad SPI透過六條線路的並行傳輸,大幅提升資料吞吐量,滿足現代嵌入式系統對速度與效能的需求。本文透過ZEROPLUS邏輯分析儀實測Quad SPI通訊,深入解析訊號波形與時序特性,驗證資料傳輸的可靠性與正確性。透過實際案例,我們揭示主控端於CLK下降緣取樣的設計考量,結合規格書分析Flash晶片輸出延遲(tCLQV)對時序的影響,闡述下降緣取樣如何提升資料穩定性與通訊精確度。此外,本文整合多通道訊號監控、時序測量與封包分析,展示邏輯分析儀在韌體驗證、通訊除錯及晶片相容性測試中的關鍵價值,為嵌入式系統開發提供實證依據與高效解決方案。

|

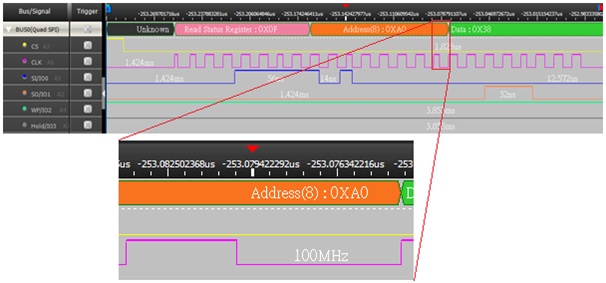

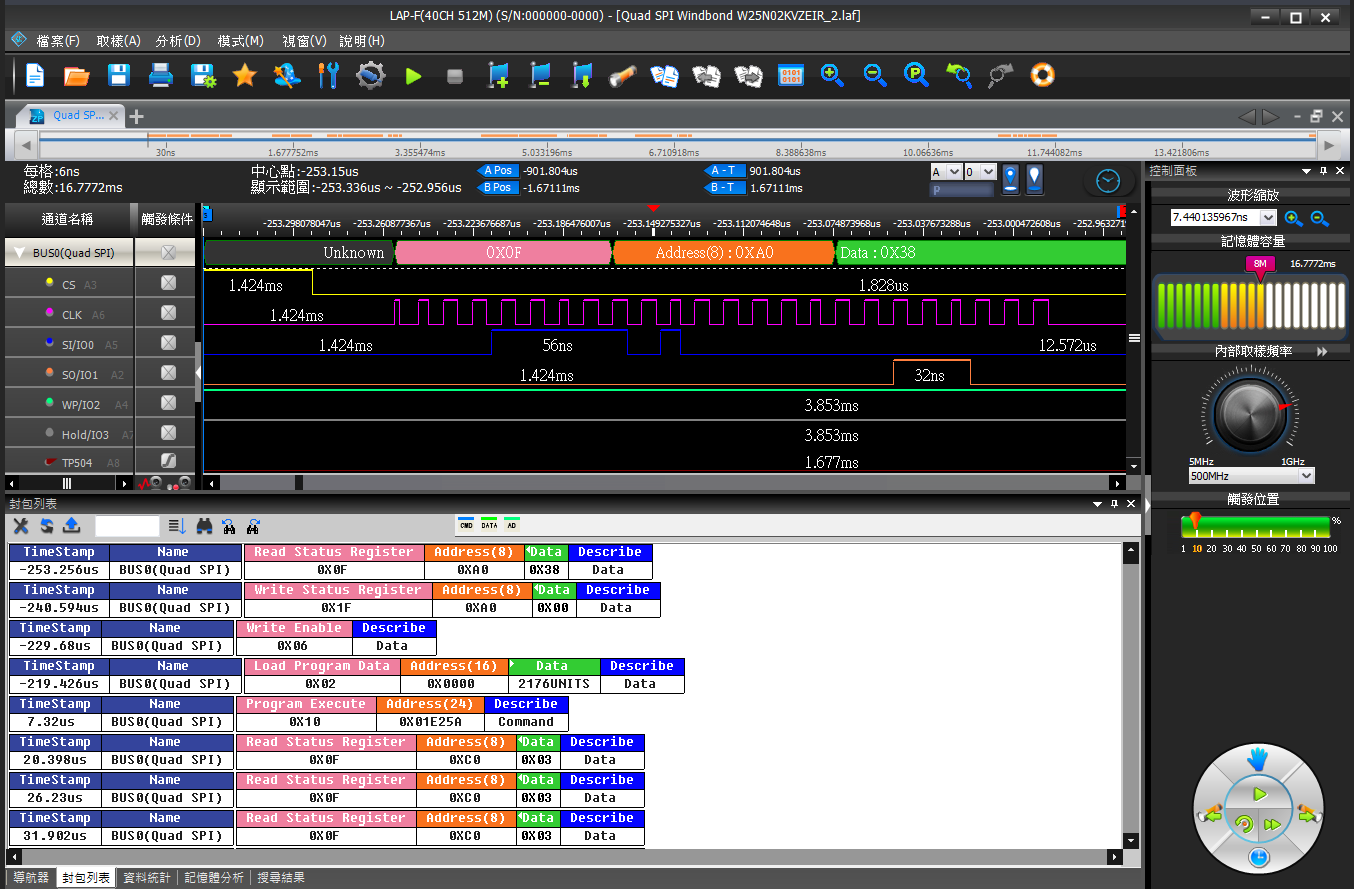

本次實測採用ZEROPLUS邏輯分析儀捕捉Quad SPI訊號波形,精準分析時序特性,確保資料位元傳輸符合外部快閃記憶體規範。內建解碼器可直接解析訊號,將其轉為可讀的數值與文字,免去工程師手動解讀的繁瑣過程。實測結果顯示:

指令解碼:完整解析Read/Write指令,如0x0F(讀取)、0x02(主程式數據)、0x06(寫入啟用)。

欄位解釋:清晰呈現地址與資料,如Address: 0xA0、Data: 0x38。

高頻分析:適用於Quad SPI高速通訊100MHz分析。

資料驗證:確認程式資料與後續Read Status Register的一致性。 |

|

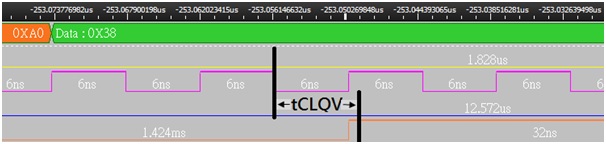

透過分析,我們觀察到主控端於CLK下降緣進行資料取樣,顯示其設計考量了Flash晶片於上升緣輸出資料的穩定時間。下降緣取樣不僅提升資料可靠性,還增強時序容忍度。此特性可透過邏輯分析儀與協定解碼進行驗證,為高速通訊除錯提供明確依據。

進一步參考規格書,Flash晶片的資料輸出延遲(tCLQV)常超出CLK半週期(tCH或tCL)。若主控端於上升緣立即取樣,可能因資料未穩定而誤判。因此,系統設計多將取樣時機延至下降緣,以增加資料建立時間並提升通訊準確性。此現象在高速操作下尤為顯著,設計時應參考Flash datasheet的時序參數,並以實測驗證系統可靠性。

此案例採用Winband W25N02KV,tCLQV=7ns,實際量測值為6ns,因此符合規範。 |

|

ZEROPLUS邏輯分析儀不僅是測試工具,更是嵌入式系統開發中不可或缺的「可視化證據」。 |

|