|

| [2015-09-17] |

Protocol Analyzer S/PDIF_V1.25.01 軟體正式發行 |

修改項目: 1. 改變匯流排頻率為2.8224MHz 或 3.0720MHz時,主程式當機。 修改前:改變匯流排頻率為2.8224MHz 或 3.0720MHz時,主程式當機。 修改後:改變匯流排設定頻率,主程式不再當機。 【下載】

|

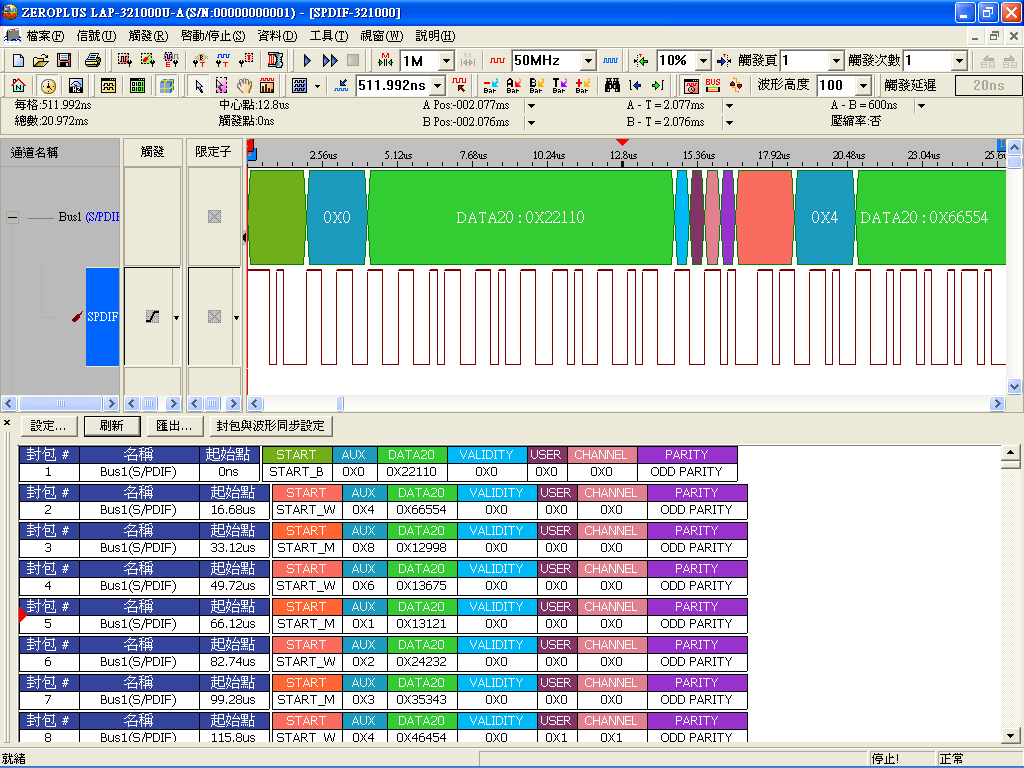

S/PDIF在硬體接腳上僅使用一條訊號作為傳輸,而訊號頻率方面目前有三種固定頻率,分別為:2.8224 MKZ、3.072MKZ和2.048MKZ)。一組S/PDIF串列協定分析通常由32個Frame至192個Frame組成,而每一個Frame中還包含著兩個Sub Frame。 每個Sub Frame長度為32 Bits,由Start、AUX Data、Audio Data、Validity、User、Channel、Parity組成: Start bit:可區分成Last cell 0及Last cell 1兩種,每一種Last cell都有Start-B、Start-M及Start-W。 AUX Data:分為24bits解碼(4-7bit為解碼代碼)及20bits解碼(4-7bit為無效略過)兩種。 Audio Data:分為24bits解碼、20bits解碼及16bits解碼三種: 16bits解碼:Data為12bit-27bit,4bit-11bit無效。 20bits解碼:Data為8bit-27bit,4bit-7bit無效。 24bits解碼:Data為4bit-27bit。 Validity:有效位元,若該位元V=0表示Data在此Sub Frame有效,若V=1則表示在此Sub Frame無效。 User:使用者自行定義標記。 Channel:通道選擇。 Parity:同位元檢查,用來檢測每一個Sub Frame的資料是否正確。 more ~

|

|

|

|

|