## UNI/O介紹與測量分析

在資訊蓬勃的時代中,生活上所使用的3C產品也不斷的演進,例如早期的手機體積十分龐大,而且待機時間又短,透過各式各樣的匯流排協助,產品內的零件也得以進化,使得現在的手機體積小,功能又強大。當然,EEPROM也正逐漸朝這個方向演進,傳統的EEPROM讀寫控制大部分都使用SPI或IIC進行傳輸,但是若是使用SPI做為傳輸介面而言,所使用的IC腳位就需要使用四條訊號通道(SCK、CS、MOSI、MISO),甚至使用IIC做為傳輸介面也需要使用兩條訊號通道(SCK、SDA)。Microchip Technology所推出的UNI/O匯流排是一種僅使用一條訊號通道,就可以達到EEPROM讀寫動作的控制介面,使用UNI/O匯流排的記憶體元件體積小,卻擁有更多的功能,如狀態暫存器(status register), $\frac{1}{4} < \frac{1}{2}$ 或全陣列的軟體寫入保護(software write protection for  $\frac{1}{4} , \frac{1}{2}$  or full array)、雜訊過濾,及有效的靜電放電保護功能(ESD protection),確保元件正常運作。

UNI/O是一種非同步串列匯流排,由Microchip Technology針對嵌入式系統中低速通訊部分所設計的。UNI/O僅需要一條訊號通道(SCIO)便可以在主/從裝置之間傳輸資料。

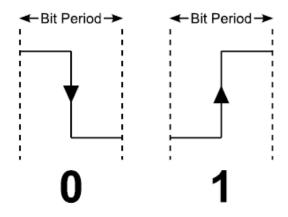

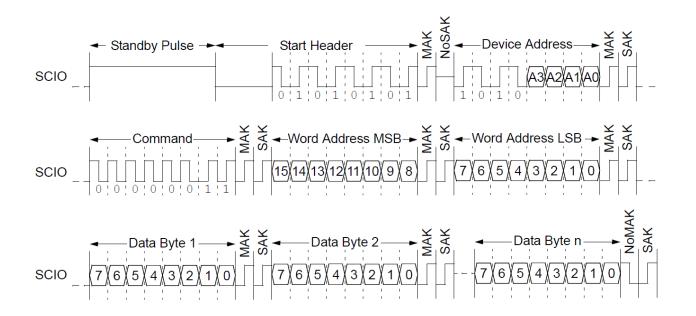

資料編碼方面,UNI/O使用曼徹斯特編碼(Manchester encoding),透過一個位元週期(bit period)內的變化來判斷該位元的邏輯狀態,如圖一所示。

▶ 圖一: IRDA SIR 封包格式

## 資料結構

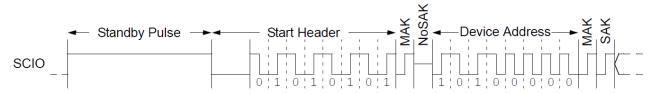

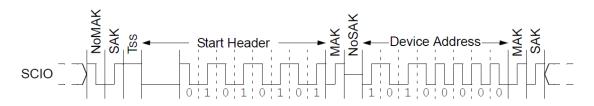

一段UNI/O訊框由數個訊號封包所組成,包含了Standby Pulse、Start Header、Device Address (Family Code、Device Code)、Acknowledge Sequence、Command、Data。

Standby Pulse:讓UNI/O進入準備狀態,會出現在Start Header封包之前,是一段持續為邏輯1的訊號,此訊號時間至少維持600us。

Start Header: 在UNI/O規範中被定義成一個特別的byte,目的用於同步主端與從端的時脈,Start Header起始是一個邏輯0的訊號與Stabdby Pulse切割,資料為0x55,傳送Start Header byte之後會立刻傳送一組ACK作為確認之用,固定由MAK(NoMAK)及SAK(NoSAK)組成。

Acknowledge Sequence:每傳送一個byte後會傳送兩個bit的確認位元,第一個位元是MAK(Master Acknowledge),第二個位元是SAK(Slave Acknowledge)。

MAK(Master Acknowledge) 位元為1時表示Master裝置有回應,此時資料會繼續傳送。若MAK位元為0時,則無回應(以NOMAK/No Master Acknowledge 表示) 此時表示該筆資料傳送完畢。

SAK(NoSAK): 為從端送出的確認訊號,當從端送出SAK時,該位元數值為1, NoSAK的數值為0,當尚未確認哪一個從端回應或沒有從端裝置回應時,該位元為不確定狀態,因此在Start Header的NoSAK為不確定狀態。

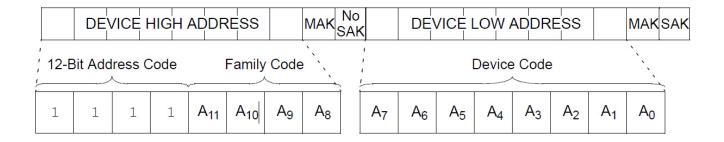

Device Address: 固定出現在Start Header之後,由Family Code及Device Code所組成。可分為8-bit address及12-bit address,用於決定Master Device與哪一個Slave Device進行傳輸。Device Address的格式由Device Address中的高四個位元來決定,當包含在Device Address中的高四個位元的數值全部為1時,Device Address的格式為12-bits Device addrsss模式,反之為8 bits Device Address模式。12-bits Device Address模式Device Address由2個Bytes組成,第一個Byte的高四位元固定為1,低四位元為Family Code,第二個Byte為Device Code;當8 bits Device Address模式Device Address,由1個Bytes組成,第一個Byte的高四位元為Family Code,低四位元為Device Code。

Family Code: Device Address中的四個位元,用於表示目前通訊的裝置狀態,如記憶體、温度感測器或A/D轉換器等。

Device Code: Device Code與Family Code同樣包含於Device Address中,依照Device Address格式不同Device Code可分為四個位元或八個位元。主要用於區分在同一個Family Code底下的裝置,若Device Address為8-bit address則Device Code e為四位元,若Device Address為12-bit address則Device Code為八位元。

Command:當Master裝置確認要傳輸的Slave裝置後會發送一個byte來表示要執行的動作類型, 一共有九種不同的命令。傳送命令時是以MSB開始發送。表一為命令列表。

| 指令名稱  | 指令編碼      | 十六進制編碼 | 説明                |

|-------|-----------|--------|-------------------|

| READ  | 0000 0011 | 0X03   | 從記憶體陣列的指定位址開始讀取資料 |

| CRRD  | 0000 0110 | 0X06   | 從記憶體陣列的當前位址讀取資料   |

| WRITE | 0110 1100 | 0X6C   | 從記憶體陣列的指定位址開始寫入資料 |

| WREN  | 1001 0110 | 0X96   | Write Enable      |

| WRDI  | 1001 0001 | 0X91   | Write Disable     |

| RDSR  | 0000 0101 | 0X05   | 讀取STATUS暫存器       |

| WRSR  | 0110 1110 | 0X6E   | 寫入STATUS暫存器       |

| ERAL  | 0110 1100 | 0X6D   | 將陣列中資料清除為0X00     |

| SETAL | 0110 0111 | 0X67   | 將陣列中資料寫入為0XFF     |

▶ 表一: UNI/O命令列表

# UNI/O訊號實機測量

孕龍科技邏輯分析儀可支援UNI/O訊號解碼,本範例中使用Microchip的MPLAB Starter Kit for Serial Memory Products (Part Number: DV243003) 開發套件做為測量目標,並使用該套件中隨附的EE-PROM 11LC160進行資料讀寫,透過孕龍科技UNI/O匯流排模組進行解碼。

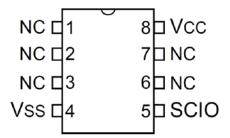

11LC160是一款擁有16K記憶容量的EEPROM,圖二為11LC160的腳位説明。

### PDIP/SOIC (P, SN)

▶ 圖二:11LC160腳位説明

由腳位説明可知,11LC160第五腳即為SCIO,故進行測量需將SCIO接上邏輯分析儀測量。

接著架設測量環境,將孕龍邏輯分析儀的AO及GND透過隨附測試鉤連接至MPLAB Starter Kit for Serial Memory Products上的SDI/SDA及GND,連接完成如圖三所示。

圖三:測量環境連接完成

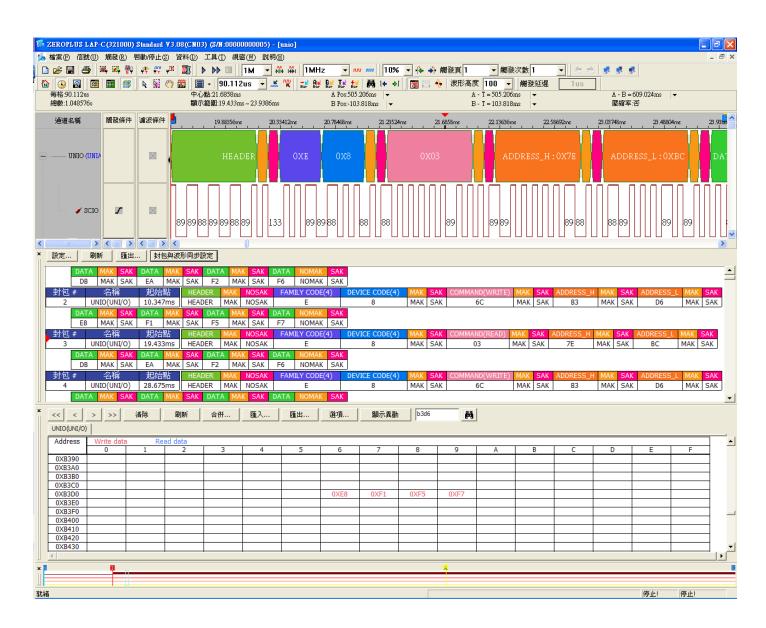

連接完成後便可以開啟孕龍邏輯分析儀軟體進行訊號測量(邏輯分析儀操作方式請參閱孕龍科技網站www.zeroplus.com.tw),擷取完成波形如圖四所示

▶ 圖四: UNI/O訊號擷取完成

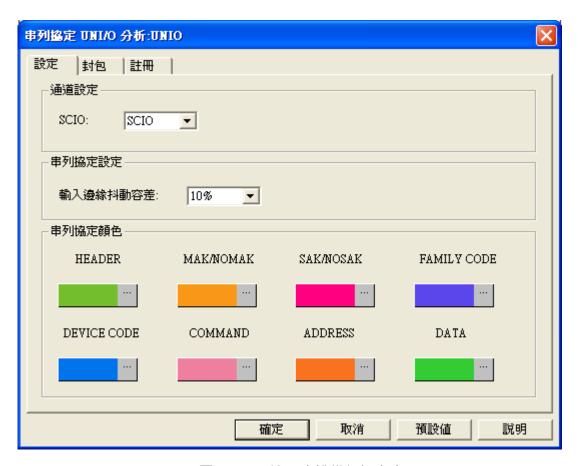

孕龍科技邏輯分析儀UNI/O匯流排模組除了可自動分析訊號封包之外,還可依照訊號內容自行設定輸入邊緣抖動容差。

▶ 圖五: UNI/O匯流排模組設定畫面

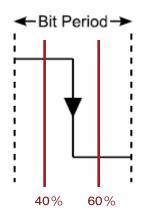

邊緣抖動容差:設定曼徹斯特編碼的位元週期中間解碼的變化緣偏移範圍,預設為10%,即表示在位元週期內40%到60%範圍內判斷變化緣。該選項的設定值是5%、10%和 15%。

▶ 圖六:邊緣抖動容差示意

隨著消費性電子產品體積縮小的趨勢,產品內部的電路元件也必須順應這股潮流,由Microchip所推出的UNI/O匯流排便是很好的範例,以往使用EEPROM傳輸時大部分都使用IIC或SPI,但是兩者在IC腳位上需佔據較多PIN腳,無法再進一步縮小電路體積,而UNI/O匯流排僅需一根SCIO腳就可以達到資料傳輸的目的,能使得更多電子產品可擁有更小巧的體積,更強大的功能。

Microchip 記憶體部門產品行銷經理Alex Martinez認為當小尺寸的微控制器及儲存裝置逐漸受到注意時,UNI/O系列是另外一種選擇,它可給予工程師一種小型化且低成本的選擇,可以讓客戶更容易的設計電路及硬體開發。

孕龍科技邏輯分析儀推出了七十多種匯流排解碼模組,針對研發工程師在分析匯流排訊號時,可透 過軟體自動解碼功能縮短開發專案的時間,及早讓商品問世,面對各種數位訊號時,不需要以人工 的方式來解碼欲分析的訊號。關於更多孕龍邏輯分析儀介紹請至孕龍科技網站www.zeroplus.com.tw

#### 參考資料:

http://techtrain.microchip.com/webseminars/ArchivedDetail.aspx?Active=160

http://en.wikipedia.org/wiki/UNI/O

http://www.microchip.com/stellent/idcplg?IdcService=SS\_GET\_PAGE&nodeId=2542&param=en535312

\* 所有商標及所有權歸屬於原註冊商所有