# 電腦系統與串列協定解析 - 網路篇

## 前 言

電腦在現今社會中可說是人人必備，無論是工作上、娛樂上都扮演著不可或缺的角色，早期當電腦處於真空管時代時，電腦體積龐大又笨重，而且功能陽春，但是經過不段的演進至今，電腦體積不但輕巧而且效能強大，最近流行的小筆電再搭配上無線通訊技術，更是搶手。

然而會出現如此便利的技術，大部分仰賴串列協定的演進，以網路技術而言，會使用到的串列協定種類十分多樣，如MII或是Manchester（曼徹斯特碼）……等。

MII串列協定即媒體獨立介面(Media Independent Interface)，是介於PHY(Physical layer) 與 MAC layer的標準介面，它是由1995年所公佈乙太網技術規範IEEE802.3U中的一種介面。分為MII資料匯流排和MII管理資訊匯流排，而時序管理介面SMI (Serial Management Interface)也是MII的重要部分，能夠提供外界存取內部的PHY暫存器。提供內部的PHY裝置暫存器能監視PHY裝置的狀態並加以控制，特別是能控制網路埠模式的工作協調。類似MII匯流排有RMII、GMII和串列的SNI等。

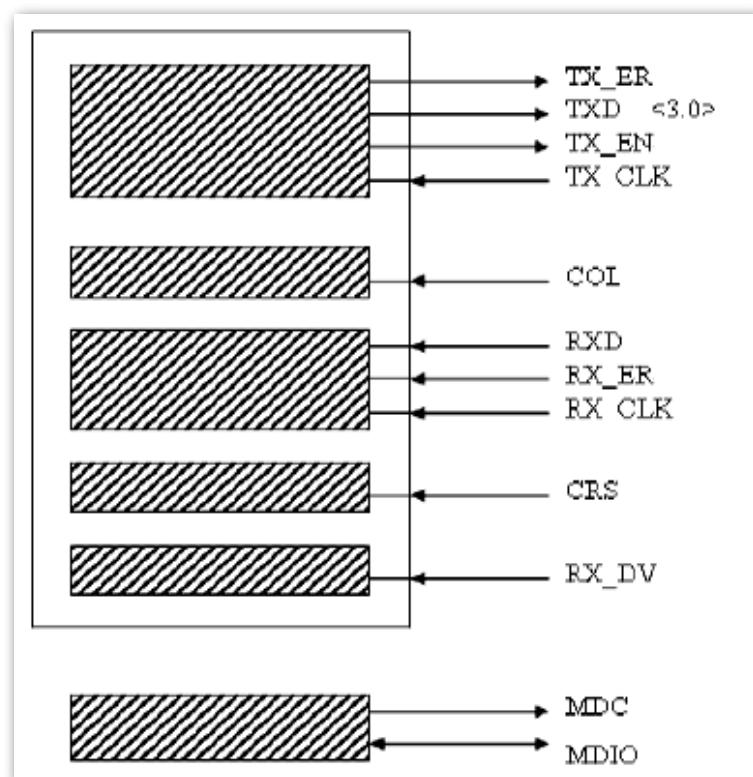

► 圖一 MII 匯流排架構

MII還有下列各項特性：

1. Media independent，介質無關、即可讓實體層使用不同的介質。

2. 支援 MAC layer 與 Physical layer 間介面的連結。

3. 支援 10Mbps 與 100Mbps data rates。

4. 支援四個位元傳送與接收。

5. 支援Physical layer 與Station management 間介面的連接。

6. 資料的傳送同步於傳送與接收頻率。

**MII動作原理及解碼說明**

MII串列協定腳位說明，如表1所示：

| Symbol                                                   | Type   | Signal Description           |

|----------------------------------------------------------|--------|------------------------------|

| <b>TXD3</b><br><b>TXD2</b><br><b>TXD1</b><br><b>TXD0</b> | Output | Transmit Data                |

| <b>TX_ER</b>                                             | Output | Transmit Error               |

| <b>TX_EN</b>                                             | Output | Transmit Enable              |

| <b>TX_CLK</b>                                            | Input  | Transmit Clock               |

| <b>RXD3</b><br><b>RXD2</b><br><b>RXD1</b><br><b>RXD0</b> | Input  | Receive Data                 |

| <b>RX_DV</b>                                             | Input  | Receive Data Valid           |

| <b>RX_ER</b>                                             | Input  | Receive Error                |

| <b>RX_CLK</b>                                            | Input  | Receive Clock                |

| <b>COL</b>                                               | Input  | Collision Detected           |

| <b>CRS</b>                                               | Input  | Carrier Sense                |

| <b>MDIO</b>                                              | I/O    | Management Data Input/Output |

| <b>MDC</b>                                               | Input  | Management Data Clock        |

► 表一 MII 腳位說明

◆ MII發送時序

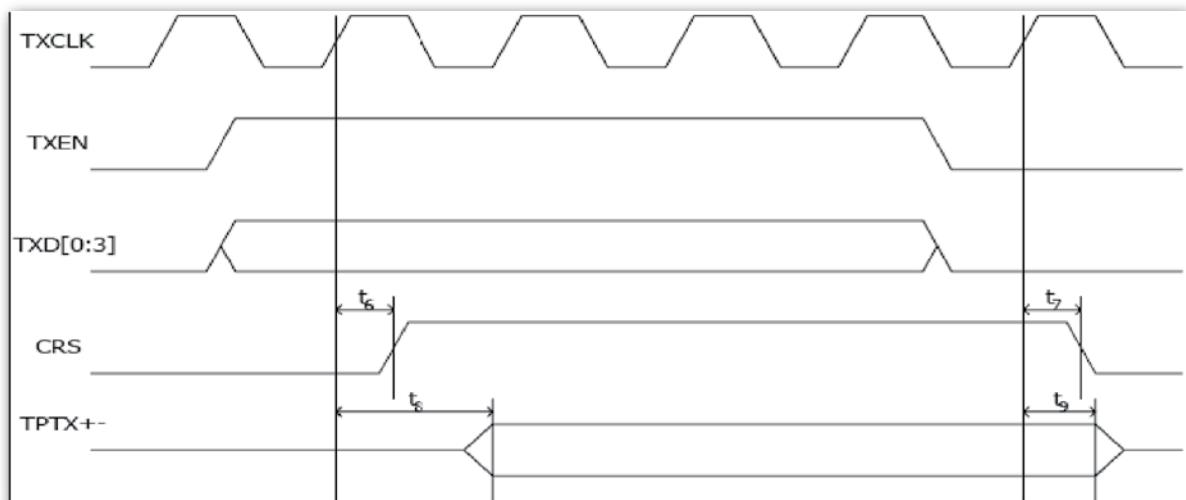

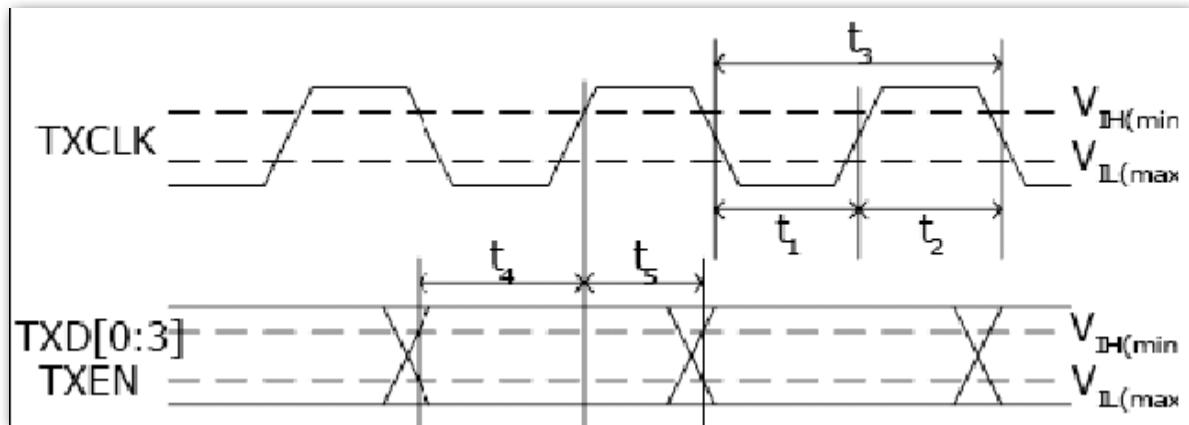

► 圖二 MII 發送時序圖

圖二中各項時序說明請參閱表二：

| 符號 | 描述                          |         | 最小  | 典型  | 最大   | 單位 |

|----|-----------------------------|---------|-----|-----|------|----|

| t1 | TXCLK高電位脈波寬度                | 100Mbps | 14  | 20  | 26   | ns |

|    |                             | 10Mbps  | 140 | 200 | 260  | ns |

| t2 | TXCLK低電位脈波寬度                | 100Mbps | 14  | 20  | 26   | ns |

|    |                             | 10Mbps  | 140 | 200 | 260  | ns |

| t3 | TXCLK週期                     | 100Mbps |     | 40  |      | ns |

|    |                             | 10Mbps  |     | 400 |      | ns |

| t4 | TXEN, TXD[0:3]設置為TXCLK上升緣   | 100Mbps | 10  | 24  |      | ns |

|    |                             | 10Mbps  | 5   |     |      | ns |

| t5 | TXEN, TXD[0:3]在TXCLK上升緣之後有效 | 100Mbps |     | 10  | 25   | ns |

|    |                             | 10Mbps  | 5   |     |      | ns |

| t6 | TXEN取樣到CRS為高準位              | 100Mbps |     |     | 40   | ns |

|    |                             | 10Mbps  |     |     | 400  | ns |

| t7 | TXEN取樣到CRS為低準位              | 100Mbps |     |     | 160  | ns |

|    |                             | 10Mbps  |     |     | 2000 | ns |

| t8 | 傳輸延遲                        | 100Mbps | 60  | 70  | 140  | ns |

|    |                             | 10Mbps  |     |     | 400  | ns |

| t9 | 取樣在Frame後段無效的TXEN           | 100Mbps |     | 100 | 170  | ns |

|    |                             | 10Mbps  |     |     |      | ns |

► 表二 發送時間表

- TX\_CLK : 是一個連續不斷的頻率，來自Physical layer，將做為TXD、TX\_EN、TX\_ER 同步的參考訊號，在10 Mbps 時，TX\_CLK 為 2.5MHZ；在100 Mbps時，TX\_CLK 為 25MHZ。

- TXD <3:0> : 是4-bit 的資料，傳送時必須與TX\_CLK同步，當TX\_EN致能後，TX\_D在Physical medium 的資料才算有意義，否則TX\_D 是無意義的。TX\_D<0>是Least Significant Bit (LSB)。

- TX\_EN : 當所有的Nibbles 都經由 MII 傳送到 Physical medium時，TX\_EN都必須是在致能的狀態。TX\_EN傳送時必須與TX\_CLK同步。

- COL : 非同步訊號，不需與TX\_CLK或RX\_CLK同步。當在Physical medium有碰撞發生時，COL致能直到碰撞結束(對半雙工過程有效, 全雙工無效)。

- CRS : 非同步訊號，不需與TX\_CLK或RX\_CLK同步。當Physical medium 上不管是傳送或接收資料，CRS都會致能。

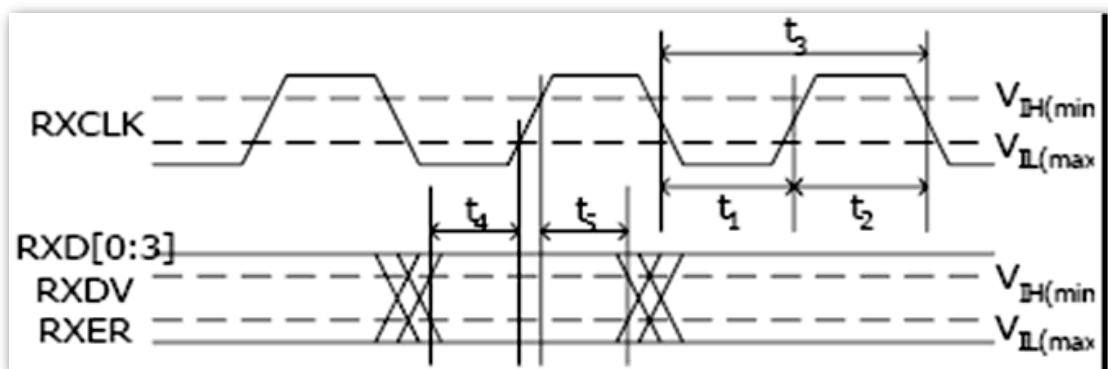

► MII接收模式

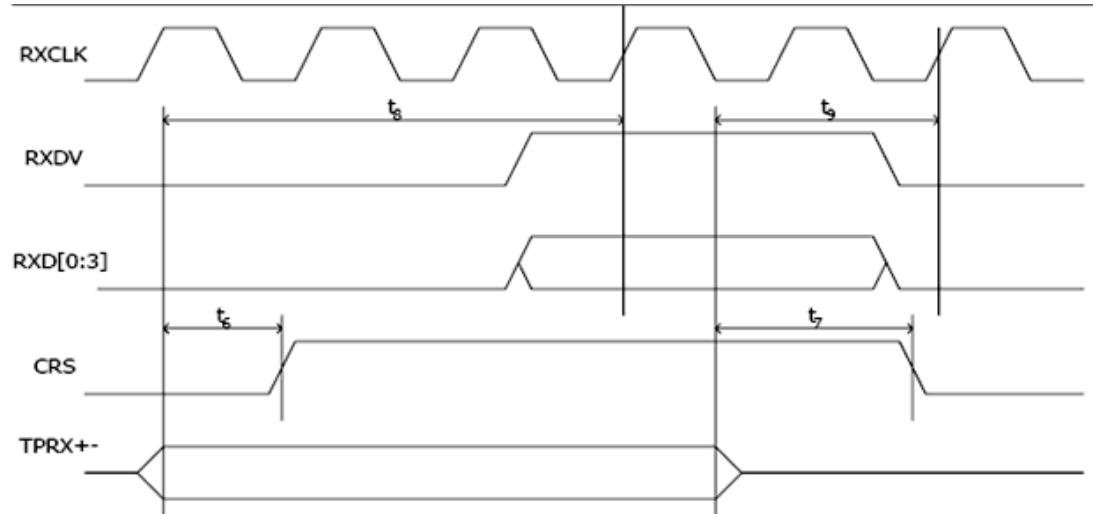

► 圖三 接收時序圖

圖三中各項時序說明請參閱表三：

| 符號 | 描述                                    |         | 最小  | 典型  | 最大   | 單位 |

|----|---------------------------------------|---------|-----|-----|------|----|

| t1 | RXCLK高電平脈寬                            | 100Mbps | 14  | 20  | 26   | ns |

|    |                                       | 10Mbps  | 140 | 200 | 260  | ns |

| t2 | RXCLK低電平脈寬                            | 100Mbps | 14  | 20  | 26   | ns |

|    |                                       | 10Mbps  | 140 | 200 | 260  | ns |

| t3 | RXCLK週期                               | 100Mbps |     | 40  |      | ns |

|    |                                       | 10Mbps  |     | 400 |      | ns |

| t4 | RXER, RXDV, RXD[0:3]設置為<br>RXCLK上升沿   | 100Mbps | 10  |     |      | ns |

|    |                                       | 10Mbps  | 6   |     |      | ns |

| t5 | RXER, RXDV, RXD[0:3]在RXCLK<br>上升沿之後有效 | 100Mbps | 10  |     |      | ns |

|    |                                       | 10Mbps  | 6   |     |      | ns |

| t6 | 在CRS高時接收幀                             | 100Mbps |     |     | 130  | ns |

|    |                                       | 10Mbps  |     |     | 600  | ns |

| t7 | 在CRS低時結束接收幀                           | 100Mbps |     |     | 240  | ns |

|    |                                       | 10Mbps  |     |     | 600  | ns |

| t8 | 檢測到RXDV邊沿時接收幀                         | 100Mbps |     |     | 150  | ns |

|    |                                       | 10Mbps  |     |     | 3200 | ns |

| t9 | 檢測到RXDV邊沿時結束接收幀                       | 100Mbps |     |     | 120  | ns |

|    |                                       | 10Mbps  |     |     | 800  | ns |

► 表三 接收時間表

- RX\_CLK：是一個連續不斷的頻率，來自Physical layer，將做為RXD、RX\_DV、RX\_ER同步的參考訊號，在10 Mbps時，RX\_CLK為2.5MHz；在100 Mbps時，TX\_CLK為25MHz。

- RXD <3:0>：是4-bit的資料，傳送時必須與RX\_CLK同步，當RX\_DV致能後，MAC接收Physical medium上的資料才算正確。RX\_D<0>是Least Significant Bit (LSB)。

- RX\_DV：訊號來自Physical medium，必須與RX\_CLK同步。RX\_D致能的範圍至少必須從SFD開始，一直到Frame的結尾。

- RX\_ER：RX\_ER傳送時必須與RX\_CLK同步，一或二個RX\_CLK時間。RX\_DV致能時，若接收有錯誤發生，則將RX\_ER致能。

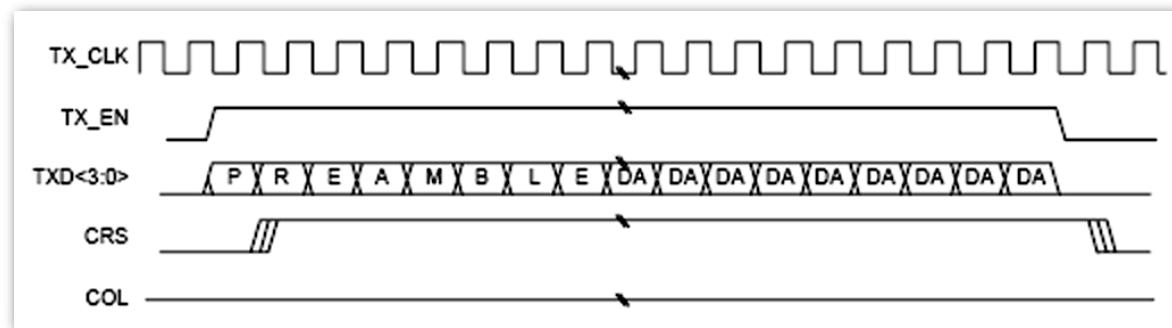

## MII發送解碼說明

MII發送共有需要8根通道，通道分別為TX\_CLK、TX\_D(0~3)、TX\_EN、TX\_ER、COL、CRS。

當TX\_EN致能為高準位表示準備發送資料，在時脈TX\_CLK的上升緣開始發送資料。資料以半位元組的方式傳輸在TX\_D通道，傳輸過程中COL為衝突檢測，當PHY媒體發生碰撞時，COL轉變為高準位狀態（如圖4及圖5所示）。調解碰撞的發生，當COL為變低時碰撞結束重新回到衝突檢測狀態。傳輸過程中CRS一直為致能狀態指示，CRS為低表示IDLE狀態，CRS為高表示傳輸狀態。

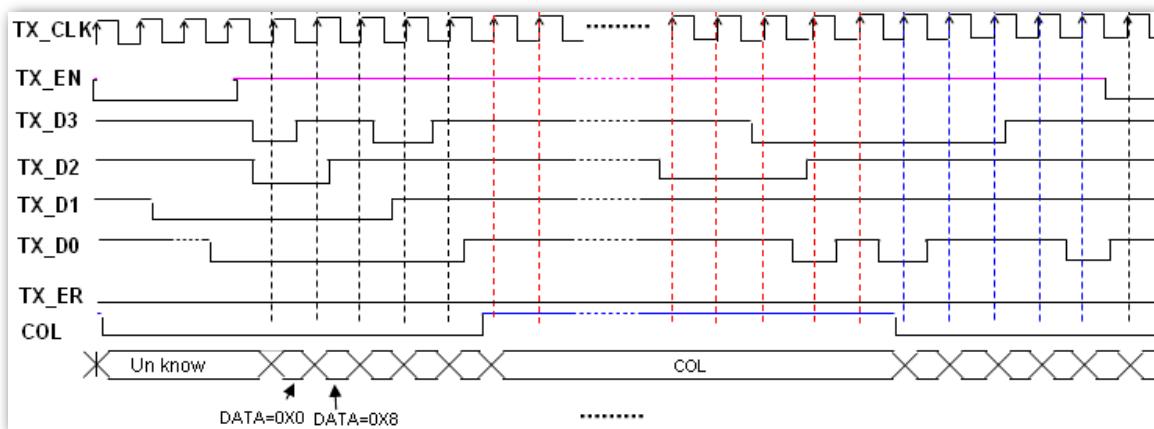

► 圖四 發送資料無碰撞

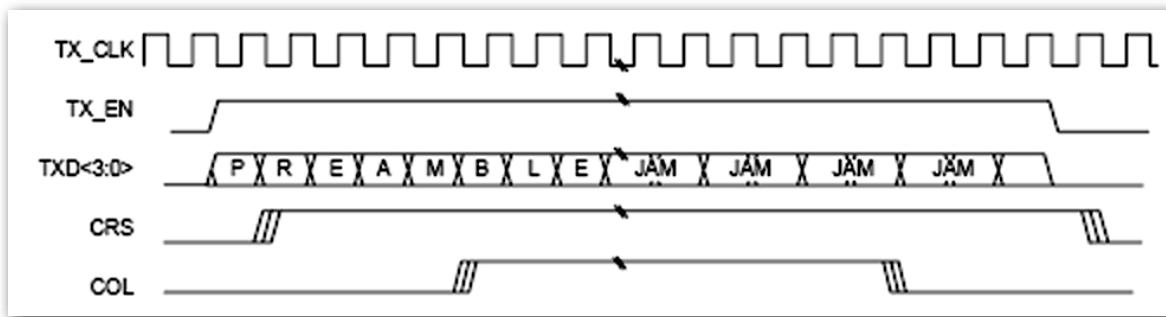

► 圖五 發送資料有碰撞

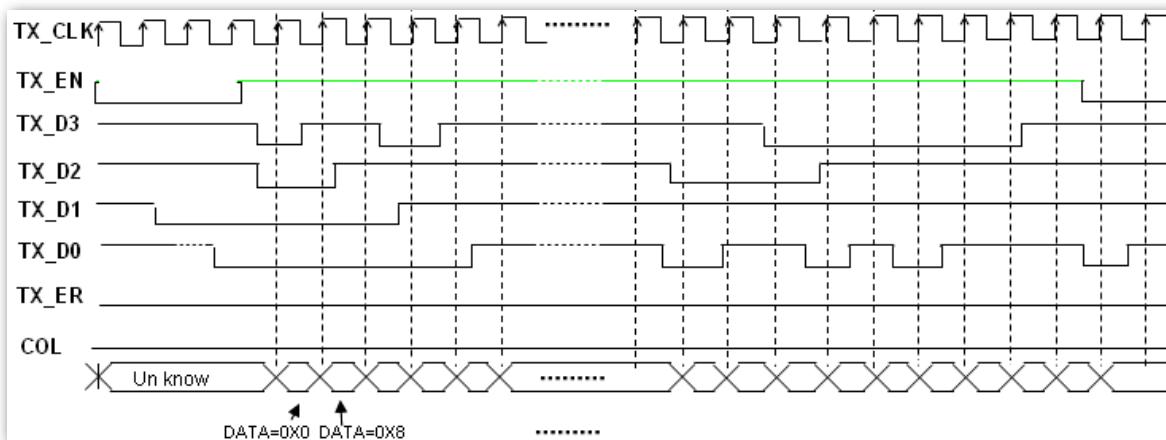

### MII發送解碼示意圖

► 圖六 發送資料無碰撞且無誤

#### 圖六說明:

當TX\_EN至能後，時脈的變化緣對應讀取資料，TX\_D3表示半位元組(HALF-BYTE)的最高位，傳輸過程中TX\_ER為低準位無變化表示發送資料無誤。COL為低準位無變化發送資料過程沒有發送碰撞，注意的是COL在半雙工傳輸過程有作用，但在全雙工傳輸時無效。

► 圖七 發送資料有碰撞

#### 圖七說明:

傳輸過程中COL發生了變化即表示傳輸過程中有碰撞發生，此狀態LA將會顯示此狀態。直到COL變化為低準位結束封包，過後狀態繼續按照TX\_EN使能判斷資料，將資料顯示為位元組或半位元組的形式。同樣COL在半雙工傳輸過程中有效，全雙工傳輸時無效。

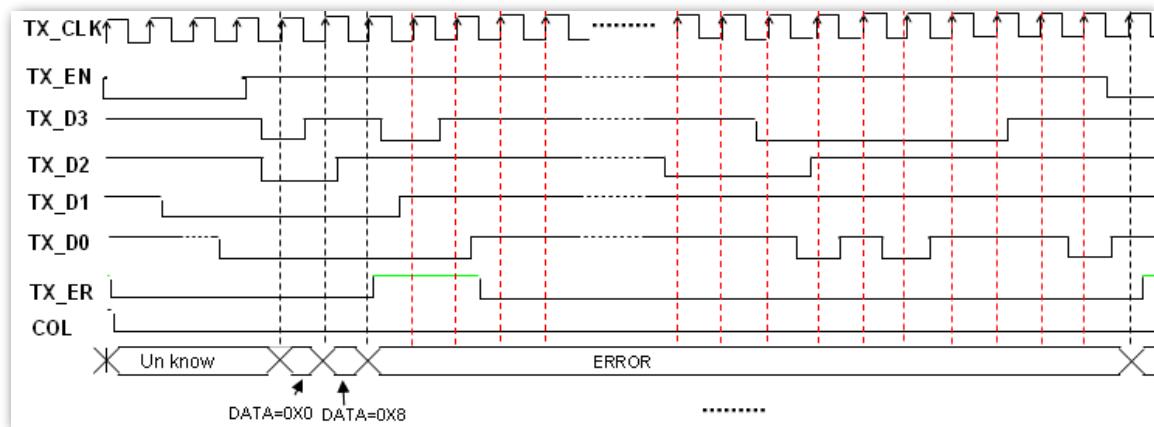

► 圖八 發送資料有誤

#### 圖八說明:

傳輸過程中TX\_ER發生變化為高準位(一般1到2個週期)，此狀態指示資料發送錯誤，有TX\_EN為高準位的狀態下資料傳輸將會判斷不正確，所以資料狀態顯示為ERROR，直到TX\_EN變化為低結束此狀態。

## 孕龍邏輯分析儀MII串列協定分析模組介紹及實際測量

孕龍科技邏輯分析儀MII串列協定分析模組提供了完整的MII訊號分析，能夠幫助使用者分析傳送狀態及接收狀態的資料狀況，同時在MII串列協定模組中也支援分析SMI協定，下面將針對各項分析功能逐一說明。

### ● MII

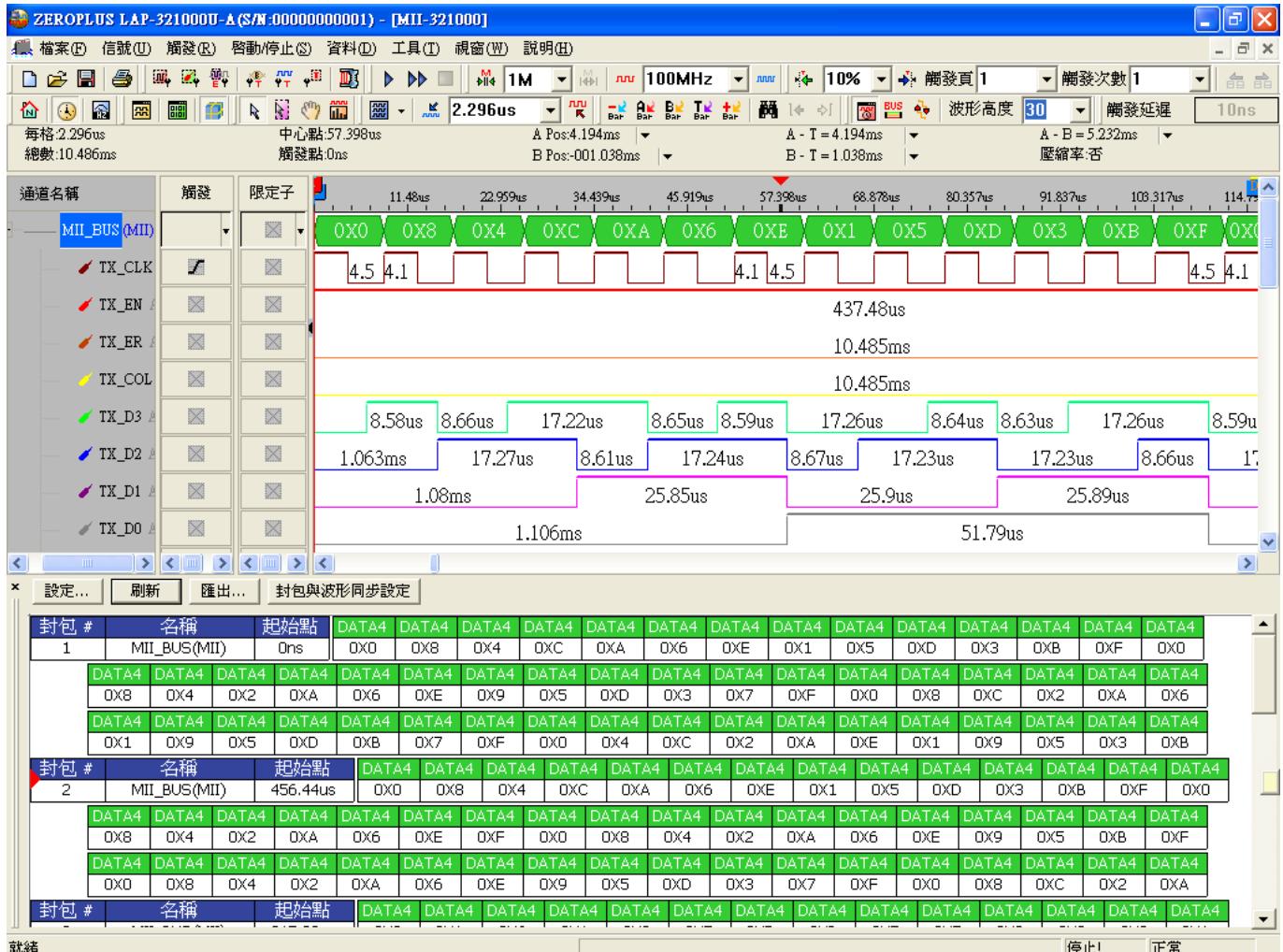

使用MII分析TX端資料時，僅需將MII各訊號腳位接妥，再進入MII串列協定分析模組設定畫面（如圖九），完成設定即可自動解碼，解碼結果如圖十所示。

► 圖九 MII串列協定分析模組設定視窗

► 圖十 使用MII串列協定模組分析結果顯示

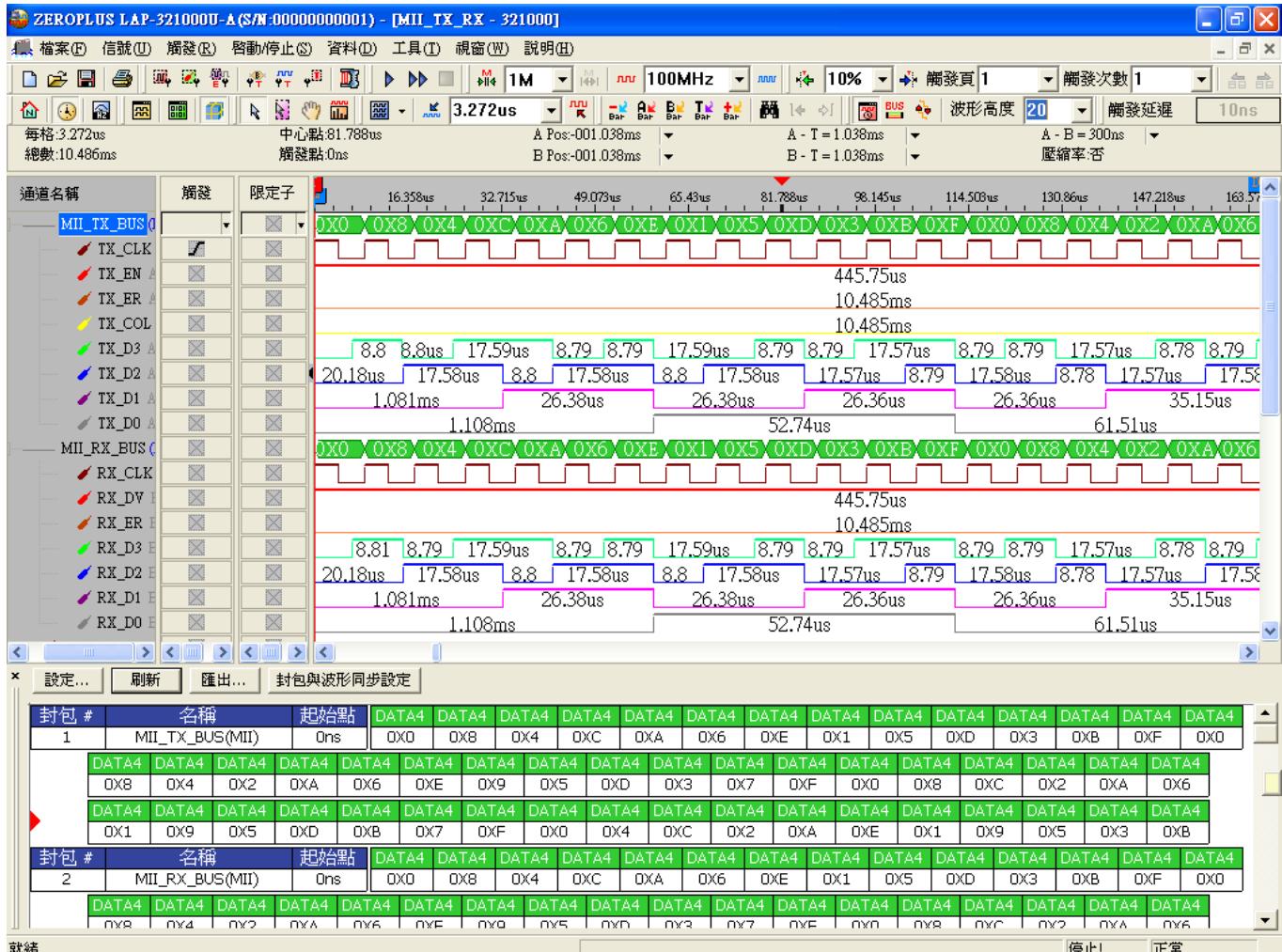

可自行設定解碼模式為TX（發送模式）或RX（接收模式），也可以自行定義資料取樣點為Clock的上升緣或是下降緣以及每一筆Data的資料長度為4bits或8bits。透過孕龍邏輯分析儀多通道特性，甚至可以同時觀測TX與RX的資料狀況，如圖十一所示。

► 圖十一 使用孕龍邏輯分析儀多通道特性同時分析MII中TX與RX之間的關係

## SMI

SMI所使用的腳位僅只有MDC及MDIO，使用MII串列協定模組進行分析僅需要在設定視窗中選擇相對應腳位即可，如圖十二所示。

► 圖十二 MII串列分析模組中分析SMI的設定畫面

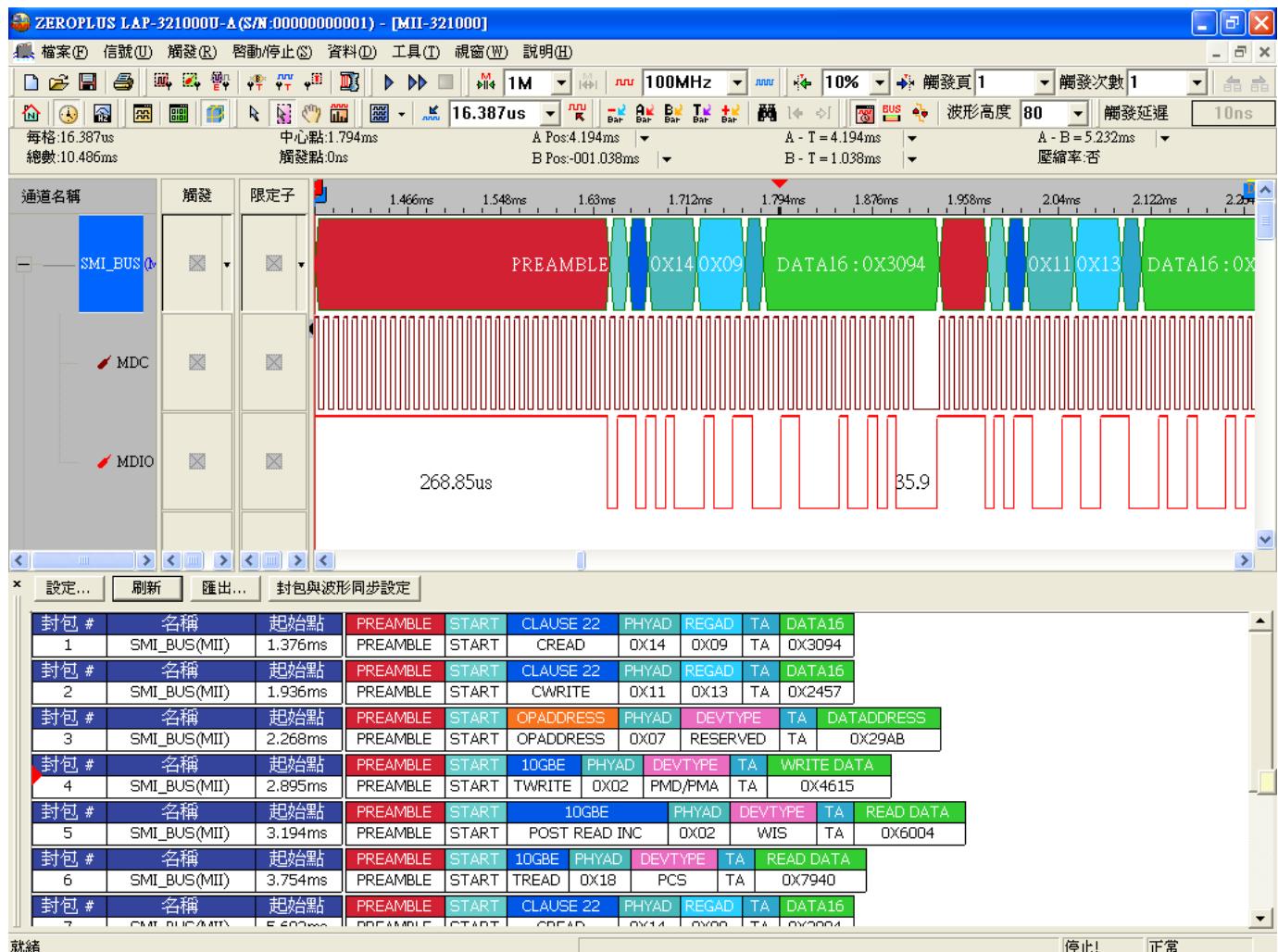

也可以在設定視窗中自行選擇使用的取樣點為Clock上升緣或是下降緣，甚至可自行設定訊號中PREAMBLE位元長度（32 ~ 255bits），設定完畢後模組會自動解碼，如圖十三所示。

► 圖十三 使用MII串列協定模組分析SMI訊號之結果顯示

**總 結**

在一個數位訊號充斥的時代，越來越多的數位訊號存在與我們生活周遭，例如手機，從早期的黑金剛，體積十分的龐大，到現在的智慧型手機。體積明顯縮小許多，而功能卻越來越強大，這些演進都是仰賴數位訊號的進步。

而孕龍科技邏輯分析儀順應這股趨勢推出了多達四十種串列協定分析模組，讓從事研發設計的工程師能夠握有一把利器，可以在研發專案中無往不利，下期將繼續以曼徹斯特碼為主題，分析這個在區域網路（LAN）中佔有重要地位的串列協定。